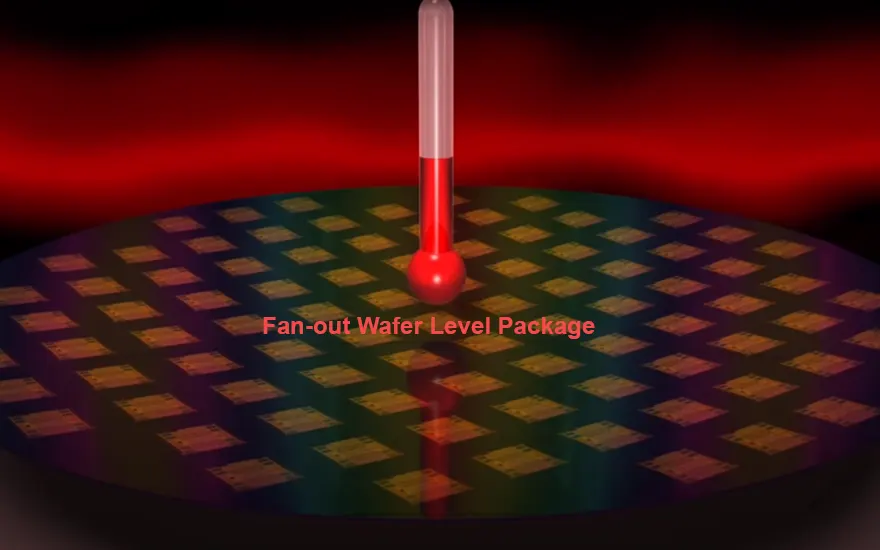

Samsung je naveo da je Exynos 2400 prvi Exynos čipset koji koristi Fan-out Wafer Level Package (FOWLP) radi poboljšanja termalnog upravljanja

Fan-out Wafer Level Package (fan-out WLP, FOWL packaging, FO-WLP, FOWLP) je tehnologija pakiranja integrisanog kruga i poboljšanje standardnih rješenja za pakiranje na razini vafera (WLP). FOWLP pruža više prostora za I/O konekcije, omogućavajući brz i efikasan prenos električnih signala.

FOWLP pruža povećanje otpornosti na toplotu od 23% pri radu na jednom jezgru i poboljšanje od 8% pri radu sa više jezgra u poređenju s flip-chip paketom, pružajući istovremeno i do 40% manji oblik i do 30% smanjenje debljine eliminacijom supstrata.

Samsung je naveo da je Exynos 2400 postigao značajna poboljšanja u upravljanju toplotom razvojem pakovanja s manjim otporom toplote, omogućavajući istovremeno manji oblik uređaja, tako da uređaj ostaje hladniji čak i tokom dugotrajnog korišćenja aplikacija i intenzivnih sesija igranja.

Prema izvještajima, Samsung Galaxy S24+ koji pokreće Exynos 2400 pruža bolje performanse u 3D Mark Solar Bay Stress u poređenju sa Samsung Galaxy S24 Ultra pokretanim sa Snapdragon 8 Gen 3 za Galaxy. Drugi izveštaji kažu da hexa-core Samsung Xclipse 940 GPU u Exynos 2400 postiže najviši rezultat od 4231 u 3D Mark Wildlife extreme testu, na nivou s Apple A17 Pro, i 2 puta bolji rezultat od Exynos 2200 koji je korišćen u Galaxy S22.

Samsung Exynos 2400 koristi vlastiti 4LPP+, koji je inferiorniji u performansama u poređenju s Snapdragonom koji koristi TSMC-ov N4P proces, ali potrošnja energije je gotovo slična, barem za GPU, tvrde izvještaji.

Princip FOWLP tehnologije

U procesu proizvodnje pločice, sa kraja poluprovodničke matrice, potrebno kolo se povlači do sloja za redistribuciju kako bi se formirao paket. Na osnovu toga, nema potrebe za pakiranjem noseće ploče, a kamoli žice i izbočina, što može smanjiti troškove proizvodnje za 30% i smanjiti debljinu čipa.

Sloj za redistribuciju u čipu skraćuje dužinu kola, što u velikoj meri poboljšava električni signal. U poređenju sa površinom poluprovodničkog čipa i površinom paketa WLCSP, površina čipa pod FOWLP tehnologijom je mnogo manja od površine originalnog pakovanja.

Zbog toga se može dovršiti više dizajna pinova ili se površina poluprovodničkog čipa nakon pakovanja može znatno smanjiti kako bi se zadovoljila potražnja za minijaturizovanim čipovima. Kao rezultat toga, nekoliko prolaznih silikonskih prolaza (TSV: Through-Silicon Via), koji su prvobitno zahtijevali visoke troškove proizvodnje, evoluirali su da integrišu različite komponente kroz tehnologiju pakovanja i minijaturizovanu SiP (System in Package) tehnologiju pakovanja.

Da bi se formirao sloj za redistribuciju, proces pakovanja mora biti uveden u prednji proces pločice, čime se takođe razbijaju inherentne barijere između front-end procesa i back-end procesa. Za proizvođače čipova je veoma važno kako postići konzistentnu tehnologiju procesa (Full Turnkey). Pod ovim, industrija livnice ambalaže i industrija materijala za pakovanje mogu imati ključno pitanje da li mogu da prežive. Stoga, za svijet poluprovodnika u budućnosti, odlučujuće sredstvo nije samo sposobnost da se poboljšaju 5nm i 3nm procesi, već konzistentna procesna tehnologija koja je proširena na prednje i zadnje strane.

Jednostavno rečeno, FOWLP je nova metoda kombinovanja više matrica iz heterogenih procesa u kompaktno pakovanje. Razlikuje se od tradicionalne operacije Silicijum Interposer (Silicon Interposer).

(IT mixer)